如何在CST中进行HSPICE仿真

CST的电路是支持IBIS和SPICE模型的,这个大家都知道。但是,SPICE模型仅限于控制符为.subckt,就是黑盒子式的子电路模型。这期我们看看更多的未直接支持的情况,比如HSPICE。

HSPICE的输入是一个.sp文件,包含电路的线路信息“netlist”,也叫Input netlist file或SPICE netlist。

举个传输线仿真的HSPICE例子:

* Stripline circuit

.Tran 50ps 7.5ns

.OPTION post Probe

VIN 1 0 PWL 0 0v 250ps 0v 350ps 3.3v

Rsource 1 2 50

Tfirst 2 0 3 0 ZO=50 TD=0.17ns

C2 3 0 2p

Tsecond 3 0 4 0 ZO=50 TD=500ps

Rtermination 4 0 50

.Probe v(1) v(2) v(3) v(4)

.End

注意,这个.sp案例中的控制符是.OPTION,其他可能用到的控制符包括.Tran,.PARAM, .INC, .LIB,.MODEL. 等等。我们在每一句后面加上解释:

* Stripline circuit 带星的是信息, comment而已

.Tran 50ps 7.5ns 瞬态仿真7.5纳秒

.OPTION post Probe 控制部分:开始

VIN 1 0 PWL 0 0v 250ps 0v 350ps 3.3v VIN是个线性电压源,位于线路节点1和0(地)之间,t=0时 V=0V, t=250皮秒时,V=0V,t=350皮秒时,V=3.3V。PWL是piecewise linear source, 就是不同时间段不同信号。

Rsource 1 2 50 节点1和2之间的内阻50

Tfirst 2 0 3 0 ZO=50 TD=0.17ns 节点2和3之间传输线,阻抗50欧,延时0.17ns;

C2 3 0 2p 节点3和地之间的电容C2;

Tsecond 3 0 4 0 ZO=50 TD=500ps 又一个传输线;

Rtermination 4 0 50 负载阻抗50欧

.Probe v(1) v(2) v(3) v(4) 在四个线路节点1234放探针

.End 结束

然后我们想一想这个电路如果画出来应该是什么样的?用CST的电路模块画大概是这样的(示意拓扑而已):

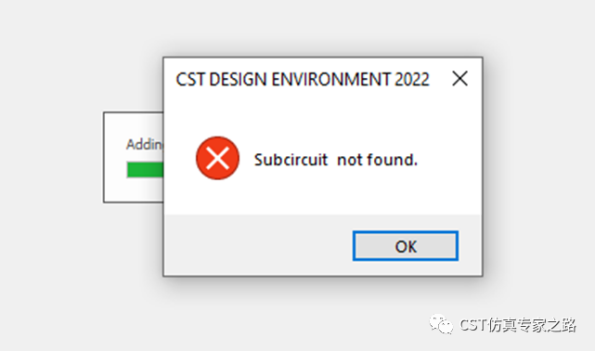

如果把这个.sp文件拖拽到CST中,则报错“Subcircuit not found”,也就是我们刚才说的,目前CST只支持子电路,而这个HSPICE是包含仿真设置的文件,并不是个单纯子电路。

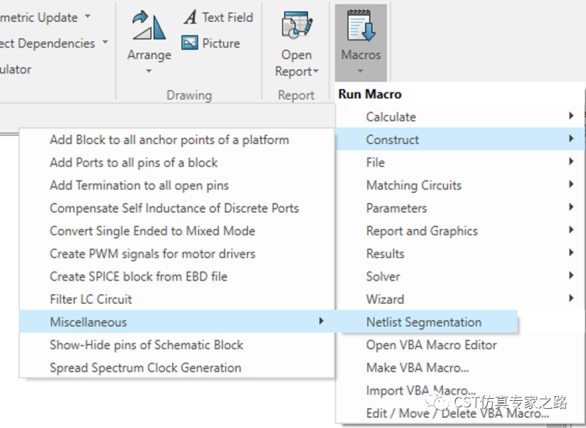

那么问题来了,我们如何将这个.sp文件拆成子电路和仿真设置,然后用在CST的电路仿真呢?答案是用到SPICE分割宏工具:

Browse选中.sp文件,定义想要提取的子电路节点(可以很多个):

这里的circuit negative filter是负过滤,意思是我们不让subcircuit包括某些toplevel的内容,一般都是电压源,电流源,内阻。

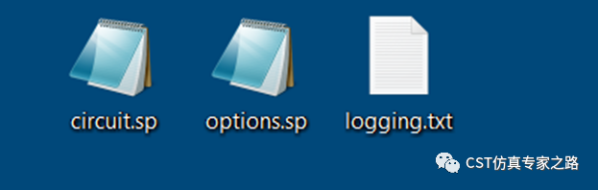

这样就把HSPICE拆成了控制文档和电路文档两部分了,还有个log:

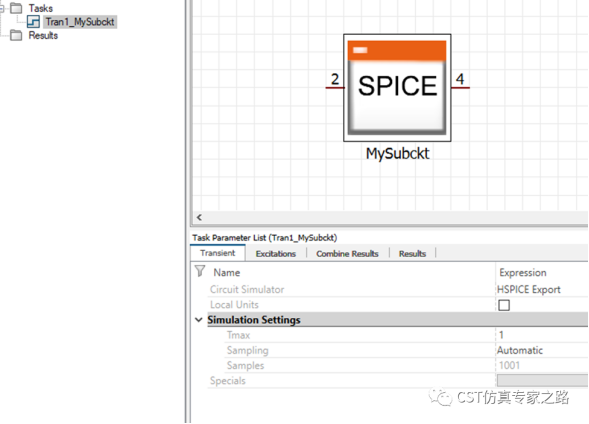

运行宏的CST电路中自动导入了这个子电路SPICE,自动添加了Tran瞬态任务,自动选好“HSPICE导出“的仿真模式:

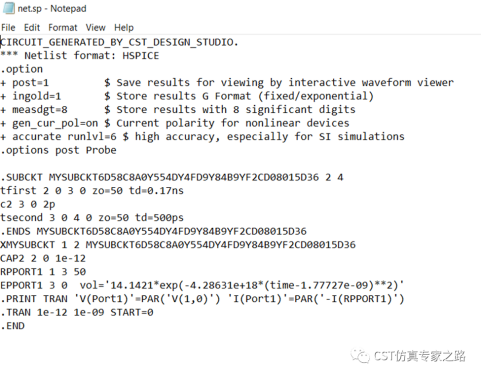

拆分的几部分SPICE内容:

有人可能问了,这不是已经导出SPICE了吗?为什么还要Tran任务HSPICE Export?这是因为用户可以在CST这里继续添加其他电路部分,或者3D仿真部分,然后整体再作为HSPICE模型导出。举个例子:

随便激励个信号(比如高斯),就导出HSPICE了,位置是项目文件夹->Results->DS,打开查看:

可见HSPICE中,我们生成的OPTION内容更多,SUBCKT也更多,有端口信息,也有端口激励的信号(高斯signal),然后就可以拿去做HSPICE仿真了。

最后一点,如果CST与其他HSPICE仿真工具都有安装在同一台机器,可以用下面这个宏工具明确HSPICE.exe的位置,这样Tran任务中就会出现新的选项,可以直接调用HSPICE仿真工具仿真并返回结果,免去以上HSPICE分割和导出sp文档的步骤哦!

小结:

1. CST虽然不能直接仿真HSPICE,但是可以处理HSPICE,拆成子电路仿真;还可以配合三维电磁仿真,场路结合,电路任务,最后导出新系统的HSPICE。

2. 拆出来的或导出新的HSPICE可以直接或间接地在其他HSPICE仿真工具中使用。

3. SPICE拆分宏工具也适用于PSPICE,LTSPICE,支持其他SPICE后缀,*.cir;*.net; *.txt",可多次使用。

4. 常见场景是DDR供应商提供HSPICE用来SI仿真。

5. Knowledge base FAQ原文:QA00000071096

(内容、图片来源:CST仿真专家之路公众号,侵删)

版权与免责声明:

凡未注明作者、来源的内容均为转载稿,如出现版权问题,请及时联系我们处理。我们对页面中展示内容的真实性、准确性和合法性均不承担任何法律责任。如内容信息对您产生影响,请及时联系我们修改或删除。

-

2026-04-07

-

[行业资讯] 仿真模拟结果的准确性和可靠性,主要受哪些因素影响?

2026-04-07

-

[行业资讯] 工业领域常用的仿真软件有哪些?达索仿真软件代理商

2026-04-03

-

[ABAQUS] Abaqus怎么旋转模型?Abaqus是哪家公司的软件?

2026-04-03

-

[ABAQUS] Abaqus是免费的吗?Abaqus商用软件找谁买?

2026-04-03

-

[行业资讯] 数字孪生赋能大湾区 2026 达索智造论坛佛山启幕

2026-04-02

-

[行业资讯] 达索系统SIMULIA Abaqus线性动力学分析技术论坛

2026-04-01

-

2026-03-30

-

2026-03-30

-

[ABAQUS] Abaqus怎么看默认单位?Abaqus软件代理商介绍

2026-03-30

-

2023-08-29

-

2023-08-24

-

[ABAQUS] ABAQUS如何建模?ABAQUS有限元分析教程

2023-07-07

-

[ABAQUS] 有限元分析软件abaqus单位在哪设置?【操作教程】

2023-09-05

-

[ABAQUS] ABAQUS软件中Interaction功能模块中的绑定接

2023-07-19

-

[ABAQUS] Abaqus怎么撤回上一步操作?Abauqs教程

2024-05-01

-

[ABAQUS] abaqus里面s11、s12和u1、u2是什么意思?s和

2023-08-30

-

[ABAQUS] Abaqus单位对应关系及参数介绍-Abaqus软件

2023-11-20

-

[ABAQUS] Abaqus中的S、U、V、E、CF分别是什么意思?

2024-05-11

-

[ABAQUS] ABAQUS软件教程|场变量输出历史变量输出

2023-07-18

-

2026-04-07

-

[行业资讯] 仿真模拟结果的准确性和可靠性,主要受哪些因素影响?

2026-04-07

-

[行业资讯] 工业领域常用的仿真软件有哪些?达索仿真软件代理商

2026-04-03

-

[行业资讯] 数字孪生赋能大湾区 2026 达索智造论坛佛山启幕

2026-04-02

-

[行业资讯] 达索系统SIMULIA Abaqus线性动力学分析技术论坛

2026-04-01

-

2026-03-30

-

[行业资讯] Abaqus有Mac版本吗?Abaqus代理商思茂信息

2026-03-27

-

[行业资讯] Abaqus哪个版本比较好?Abaqus正版软件多少钱

2026-03-27

-

[行业资讯] 上课啦!达索系统SIMULIA CST核心模块及微波&天线

2026-03-25

-

[行业资讯] 达索系统于NVIDIA GTC 2026展示AI驱动的虚拟

2026-03-25

地址: 广州市天河区天河北路663号广东省机械研究所8栋9层 电话:020-38921052 传真:020-38921345 邮箱:thinks@think-s.com