CST软件探索EFT虚拟测试:从IEC标准到3D仿真实战

作者 | Wang Jieyu

电快速瞬变脉冲群(EFT)问题传统上依赖“测试-失败-整改”的循环,成本高且周期长。利用CST Studio Suite进行虚拟测试,可将EMC设计前置,实现从“被动整改”到“主动设计”的转变。

IEC 61000-4-4标准:仿真的基础

仿真的首要步骤是准确理解并复现国际标准。CST仿真能精准定义EFT波形的关键参数(如上升沿5ns、脉宽50ns)及实验等级(1-4级),为虚拟测试建立真实、可靠的基准。

核心步骤:在CST中构建EFT仿真

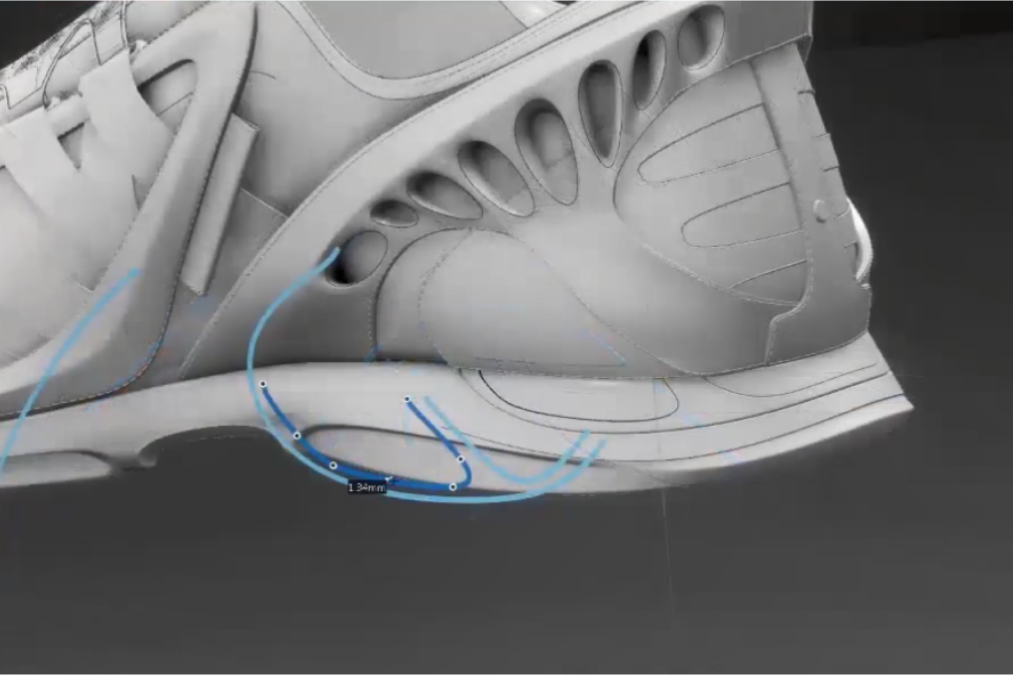

一 精准建模容性耦合夹

在CST中建立容性耦合夹的3D模型,并通过仿真提取其Z参数和耦合电容。此步骤确保了仿真模型能够真实反映实际测试环境的电磁特性。

1.1容性耦合夹3D建模

1.2 容性耦合夹的仿真结果

注:该耦合夹模型为笔者自行创建,不与任何实验室模型比对,仅用于仿真流程展示

二 构建完整的EFT仿真系统

CST解决方案的核心优势,在于其能够进行系统级的瞬态场路协同仿真,将3D电磁模型与电路无缝集成,构建完整的虚拟测试系统,而非进行孤立的部件分析。

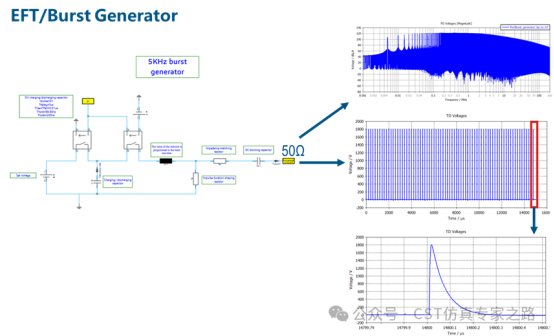

2.1 EFT脉冲源建模:我们需要根据标准定义,建立能够产生准确波形(如脉冲上升沿5ns,脉宽50ns)的EFT发生器模型。在CST component library中为用户提供了EFT/Burst Generator的电路模型。该模型符合IEC61000-4-4。

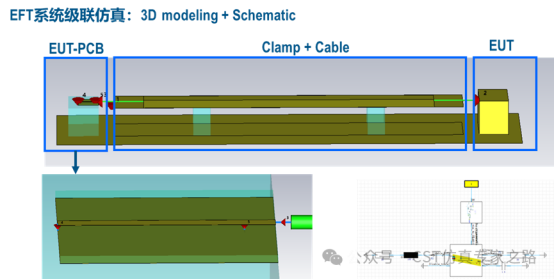

2.2 系统级联仿真:将3D模型(如耦合夹、PCB、线缆)与电路模型(EFT发生器、设备端口)进行联合仿真在CST设计环境中进行协同仿真,构建完整的虚拟测试系统。

CST仿真实战价值

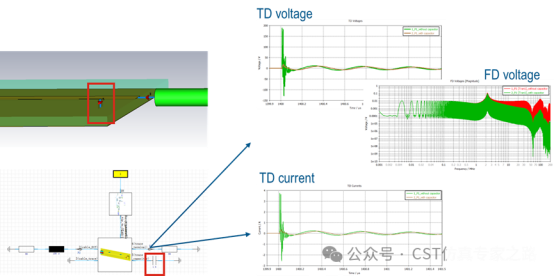

案例一:端口滤波设计优化—验证信号端口电容对EFT的影响

在CST中调整端口电容值,可直观观察时域波形变化。仿真能快速筛选最优滤波方案,避免过度设计或设计不足。仿真模型及仿真结果如下图所示:

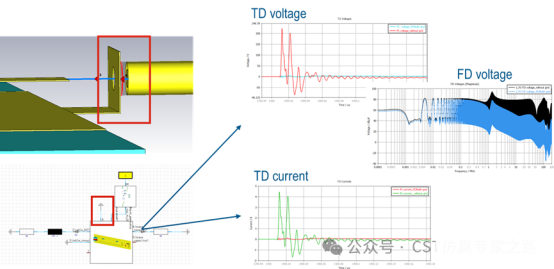

案例二:验证cable屏蔽层搭接效果对EFT的影响

CST仿真可清晰量化屏蔽层搭接质量对性能的影响。Cable屏蔽层是否接地,其抑制EFT干扰的效果差异一目了然。 仿真模型及仿真结果如下图所示:

-

[行业资讯] 当 AI 遇到 CNC:全面革新机加工运营模式

2026-04-15

-

[行业资讯] 达索系统 SIMULIA PowerFLOW 技术论坛即将

2026-04-14

-

[CST] 进行复杂的电路板(PCB)设计时,如何有效规避电磁干扰(E

2026-04-13

-

[行业资讯] 电磁场仿真工具CST studio suite正版价格多少

2026-04-13

-

[CST] CST studio suite可以仿真介电损耗吗?

2026-04-13

-

[ABAQUS] abaqus软件的主要功能?Abaqus软件正版价格

2026-04-10

-

[ABAQUS] abaqus如何定义和删除参考点如何导出和修改inp文件

2026-04-10

-

2026-04-10

-

2026-04-07

-

[行业资讯] 仿真模拟结果的准确性和可靠性,主要受哪些因素影响?

2026-04-07

-

2023-08-29

-

2023-08-24

-

[ABAQUS] ABAQUS如何建模?ABAQUS有限元分析教程

2023-07-07

-

[ABAQUS] 有限元分析软件abaqus单位在哪设置?【操作教程】

2023-09-05

-

[ABAQUS] ABAQUS软件中Interaction功能模块中的绑定接

2023-07-19

-

[ABAQUS] Abaqus怎么撤回上一步操作?Abauqs教程

2024-05-01

-

[ABAQUS] abaqus里面s11、s12和u1、u2是什么意思?s和

2023-08-30

-

[ABAQUS] Abaqus单位对应关系及参数介绍-Abaqus软件

2023-11-20

-

[ABAQUS] Abaqus中的S、U、V、E、CF分别是什么意思?

2024-05-11

-

[ABAQUS] ABAQUS软件教程|场变量输出历史变量输出

2023-07-18

-

[行业资讯] 当 AI 遇到 CNC:全面革新机加工运营模式

2026-04-15

-

[行业资讯] 达索系统 SIMULIA PowerFLOW 技术论坛即将

2026-04-14

-

[行业资讯] 电磁场仿真工具CST studio suite正版价格多少

2026-04-13

-

2026-04-07

-

[行业资讯] 仿真模拟结果的准确性和可靠性,主要受哪些因素影响?

2026-04-07

-

[行业资讯] 工业领域常用的仿真软件有哪些?达索仿真软件代理商

2026-04-03

-

[行业资讯] 数字孪生赋能大湾区 2026 达索智造论坛佛山启幕

2026-04-02

-

[行业资讯] 达索系统SIMULIA Abaqus线性动力学分析技术论坛

2026-04-01

-

2026-03-30

-

[行业资讯] Abaqus有Mac版本吗?Abaqus代理商思茂信息

2026-03-27

地址: 广州市天河区天河北路663号广东省机械研究所8栋9层 电话:020-38921052 传真:020-38921345 邮箱:thinks@think-s.com