基于Abaqus本构二次开发的板级封装结构冲击响应数值模拟

简介

科学技术的不断提高促使便携式电子产品进入到高速发展的快车道,消费者对此的需求和用途也不断扩大,这导致该类产品的可靠性要求变得更高,特别是用途多样性带来的跌落冲击响应和器件多功能、小型化造成的高功率作业以及不同的服役环境等极端工况条件。

在 2004 年,Tee 等人提出了 Input-G 方法,这一方法是将电子元器件跌落后获得的反向加速度脉冲信号作为边界条件直接施加在标准 PCB 板的四个螺栓孔的位置,除 PCB 板和其上固定的封装结构外,其于装置根据实验原理均可忽略不计。LIM 等利用 ABAQUS 显式分析模拟了寻呼机的跌落冲击动力响应;WONG 等人研究了在跌落冲击载荷下 PC 板的基本动力学原理;VARGHESE 和 DASGUPTA 发现,在诸多影响因素中,对钎料焊点冲击性能影响最为重要的是过载冲击力和应变大小。

板级封装跌落冲击

表面贴装技术在 IC 集成电路中扮演者重要的角色,是芯片与载体之间牢固的连接方法。球栅阵列封装(Ball Grid Array, 简称 BGA)形式因为自身的个体单位空间存储量高、低电感和I/O 数量多等的优势而被广泛应用。

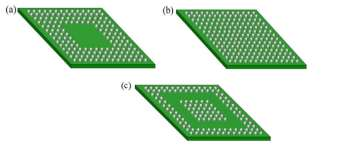

BGA 封装结构在便携式电子产品中的普遍使用使其在应用过程中面临着极端服役环境的挑战。本文根据引脚排列的 BGA 分类周边型阵列、全阵列、交错型阵列,三种不同焊点分布 (14×14) 的 BGA 封装结构在跌落冲击条件下的互连材料力学响应行为进行研究,具体分布形式如图 2-1 所示。

图 2-1 BGA 焊点分布形式

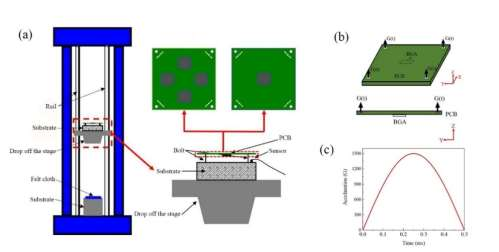

美国电子器件工程标准联合委员会(JEDEC)在 2003 年颁布了针对便携式电子产品跌落测试标准 JESD22-B111,并于 2016 年对其进行了修订,即标准 JESD22-B111A。标准中介绍了典型的跌落冲击测试实验装置,主要由导轨、跌落台和刚性基座组成;测试过程中标准 PCB 板通过四个螺栓固定在跌落台的基板上,如 Error! Reference source not found.-a 所示。数值仿真中冲击加速度脉冲的施加方式示意图如 Error! Reference source not found. 所示;在 JEDEC 标准中,推荐使用 B 类峰值为 1500G、脉冲时间为 0.5 ms 的半正弦加速度脉冲载荷曲线,如图2- 所示。

图 2-2 (a) 典型跌落冲击试验装置简图,(b) 整体模型加载方式。(c)半正弦加速度脉冲载

荷曲线

在封装结构朝下且水平跌落的条件下焊点获得的动态冲击响应比其他跌落方式获得的响应效果大,更容易失效,因此只开展了 PCB 板水平跌落的仿真内容。同时,考虑到整体模型的复杂性和计算时间,所以在数值仿真过程中仅模拟在 PCB 板中间贴装有一个 BGA 封装结构的板级模型。

3. 仿真模型建立

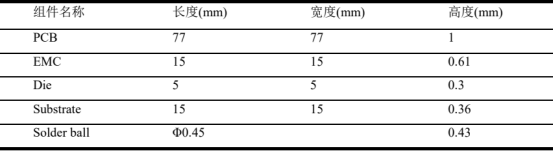

在建模过程中,PCB 板即采用 JEDEC 修订的新标准 JESD22-B111A 中规定的尺寸,并根据标准建立四螺栓孔的约束设计,根据实际应用在其中施加载荷。全局模型主要是由 EMC、Die、Substrate、Solder ball 和 PCB 5 部分构成,各组件的相关尺寸如表 3-1 所示,其中,相邻焊点之间的中心间距为 1 mm。

表 3-1 板级封装跌落模型各组件相关尺寸

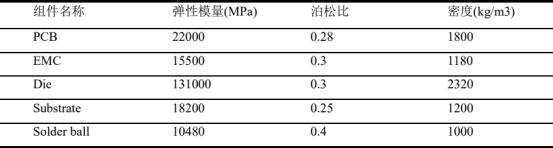

在建模过程中通过利用 Merge 技术将多个组件组合成为一个新的 Part,同时在此过程中仍然保留分界面来确保对不同组件的区分,便于指定不同的材料属性。焊点的材料属性采用Johnson-cook 本构模型参数定义,EMC 的材料属性通过 ZWT 本构模型定义,其余组件的材料参数如表 3-2 所示。

表 3-2 板级封装跌落模型各组件材料参数

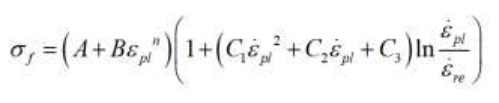

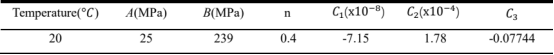

焊点采用的 Johnson-cook 本构模型如下,其中是流动应力;A 为 SAC305 焊料的屈服强度,参考应变率通过准静态实验获得是等效的塑性应变,为塑性应变率,B 和 n 分别是应变硬化系数和应变硬化指数。C1、C2、C3 是 SHPB 冲击实验得到的应变速率相关参数。

相应的参数设置如下

表 3-3 JC 本构参数

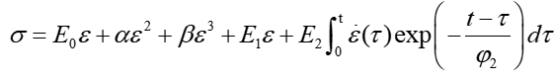

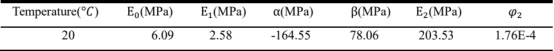

ZWT 模型用于板级冲击问题中的 EMC 材料,因为物理模型的低应变率响应部分可以用刚度E1的线性弹簧元件代替。其中E0,α,β是非线性弹簧常数; E1、E2分别为低应变率和高应变率线弹性弹簧模量, ��2是高应变率下的松弛时间。

相应的参数设置如下

表 3-3 ZWT 本构参数

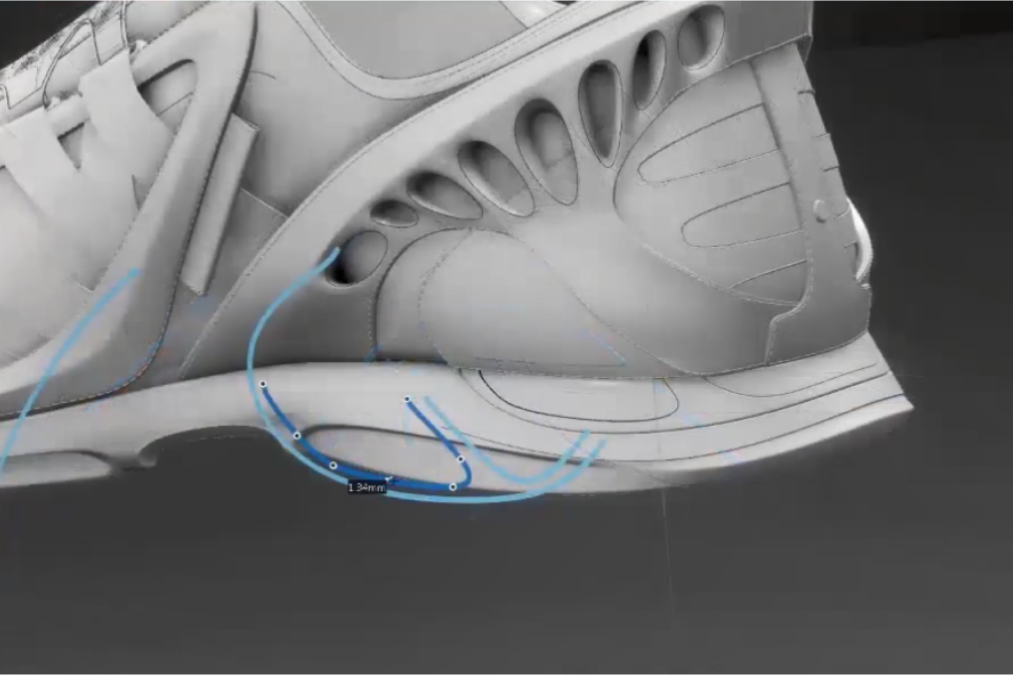

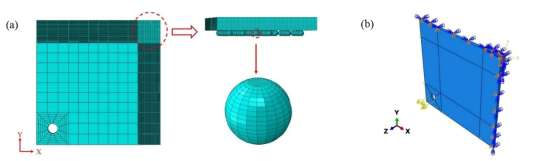

根据表 3-1 中不同组件尺寸的相关数据可以看出焊点尺寸相对 PCB 板的尺寸小很多,因此,本章节在开展过程中,对板级封装结构模型中的不同组件采用不同规格的网格尺寸,即对各组件进行切割操作来细化焊点和其接触位置的网格,粗化其他部位的网格。在单元类型选择方面,整体模型中的各组件均选择为 C3D8R 的三维实体线性减缩积分的六面体单元,如 Error! Reference source not found.-a 所示。

考虑到整个板级封装结构为中心对称结构,为了缩小计算时间并提高计算效率,本章节在开展过程中建立 1/4 模型,如图 3- 所示。同时,在 1/4 模型对称面上需要施加对称约束,即在X 对称面上施加 X 方向的平动约束和 Y、Z 方向的转动约束,在 Y 对称面上施加 Y方向的平动约束和 X、Z 方向的转动约束。

图 3-1 (a) 网格划分,(b)载荷与边界条件

对于冲击响应的加速度载荷施加方式,在仿真过程中采用 Input-G 的方法。按照该方法的使用要求,PCB 板在自由落体后获得的冲击载荷以加速度脉冲信号的形式作用在四个螺栓孔处,方向竖直向上。

4. 仿真结果与分析

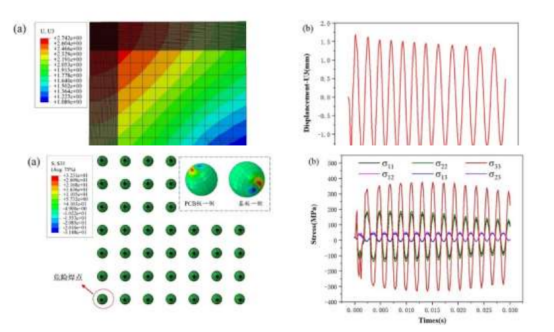

根据跌落冲击理论,贴装有 BGA 封装结构的 PCB 板在跌落冲击响应过程中主要包含两个阶段,第一阶段是 PCB 板承受半正弦加速度脉冲载荷阶段,第二阶段是加速度脉冲载荷消失后的自由振动阶段。仿真结果中 PCB 板的动态冲击位移响应云图如图 4- (a)所示,其中心节点的位移时间历程曲线如图 4- (b)所示。板级封装结构在承受半正弦加速度脉冲冲击载荷之后,当分析步时间为 1.3 ms 时,PCB 板中心位置的响应最大,绝对位移为 2.7 mm,相对位移为 1.64 mm。

图 4-1 (a) 1.3ms 时的位移响应云图,(b) 中心节点的位移时间历程曲线。

如 Error! Reference source not found. 所示为封装结构焊点阵列的法向应力云图。危险焊点的最大法向应力位于焊点与 PCB 连接的位置,且靠近 PCB 板边缘一侧,其次为焊点与基板相连的上表面,并且靠近基板中心的位置。

如 Error! Reference source not found.所示为焊点的应力与时间关系曲线,与 PCB 板垂直方向的正应力(σ33)值远大于其他分量应力,即最大应力为剥离应力,其值最大为 349.69 MPa。

图 4-2 (a)焊点阵列的法向应力云图,(b) 最危险焊点处的应力与时间关系曲线

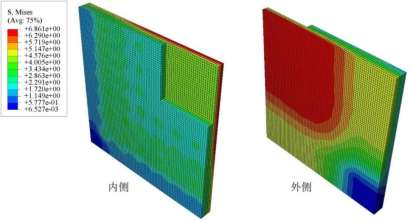

在 PCB 板位移响应的最大时刻,高分子聚合物层也发生严重变形,此时该结构的内侧和外侧应力云图如 Error! Reference source not found. 所示。从图中可明显看出,在跌落冲击载荷作用下,高分子聚合物层的最大应力发生在其中心部位,并且是位于外侧,内侧应力值较低,与芯片的相互作用较弱,对芯片的影响效果较小。

图 4-3 高分子聚合物层内侧和外侧应力云图

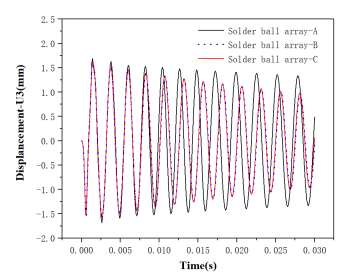

为了研究同种封装形式中不同焊点分布对整个板级封装结构的跌落冲击响应影响,在本文开展过程中依据选择了三种焊点分布不同的 BGA 型号.图 4- 所示为三种不同焊点分布类型条件下的 PCB 板的位移冲击响应情况,根据仿真计算结果,在 8ms 之前三者存在很好的重合性,但是焊点阵列 A 的位移峰值略高于焊点阵列 B、C,这主要是由于焊点阵列 B、C 对最中心焊点进行了保留,起到了约束作用,导致最大位移比去除中心焊点的 A 阵列小,相位也相应滞后。而阵列 B 与阵列 C 位移趋于一致,这反映了 3、4 层焊点对位移的影响不大。

图 4-4 不同焊点分布的 PCB 板位移冲击响应

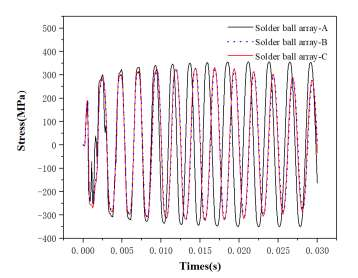

根据 Error! Reference source not found.内容,剥离应力可被视为判断焊点失效的主要依据,图 4- 为三种不同焊点分布情况下危险焊点的剥离应力曲线图。同 PCB 板的位移冲击响应类似,焊点阵列 B、C 危险焊点的剥离应力也存在明显的滞后现象,并且其最大应力小于阵列 A 的349.69 MPa。证明在相同的载荷作用下,焊点阵列 A 更容易破坏。

图 4-5 不同焊点分布危险焊点剥离应力曲线图,(a) 焊点阵列 B,(b) 焊点阵列 C.

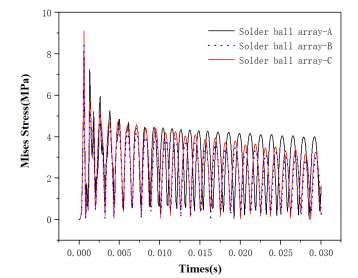

在相同的冲击载荷作用下,不同的焊点分布形式对高分子聚合物层的影响如图 4- 所示。当响应时间到达 0.6ms 时,焊点阵列 A、B、C 引起的高分子聚合物层的 Mises 应力均达到最大值,并且在 5 ms 之后,焊点阵列 B、C 相对焊点阵列 A 出现滞后现象,同时,使得高分子聚合物层的 Mises 应力下降速度加快,其应力值小于焊点阵列 A。

图 4-6 不同焊点分布对高分子聚合物层的影响

5. 结论

本文通过在 BGA 封装结构中综合应用焊点材料和高分子聚合物材料的本构模型,根据JEDEC 在 2016 年修订的新版针对便携式电子产品跌落测试标准 JESD22-B111A 展开板级封装的跌落冲击仿真工作,采用 Input-G 方式,使用峰值为 1500G、脉冲时间为 0.5ms 的半正弦加速度脉冲载荷,整体模型根据对称性建立 1/4 模型。

结果显示远离 PCB 板中心点的角焊点所受应力最大,为最易破坏的危险焊点,并且垂直于 PCB 板方向的正应力为剥离应力,此外,高分子聚合物层的最大应力发生在其外侧的中心位置。在相同的载荷作用下,焊点阵列 A 所受应力最大,B、C 阵列所受应力较小且十分接近,说明最里层焊点在此时起着十分明显的约束作用。

资料来源:达索官方

-

[行业资讯] 当 AI 遇到 CNC:全面革新机加工运营模式

2026-04-15

-

[行业资讯] 达索系统 SIMULIA PowerFLOW 技术论坛即将

2026-04-14

-

[CST] 进行复杂的电路板(PCB)设计时,如何有效规避电磁干扰(E

2026-04-13

-

[行业资讯] 电磁场仿真工具CST studio suite正版价格多少

2026-04-13

-

[CST] CST studio suite可以仿真介电损耗吗?

2026-04-13

-

[ABAQUS] abaqus软件的主要功能?Abaqus软件正版价格

2026-04-10

-

[ABAQUS] abaqus如何定义和删除参考点如何导出和修改inp文件

2026-04-10

-

2026-04-10

-

2026-04-07

-

[行业资讯] 仿真模拟结果的准确性和可靠性,主要受哪些因素影响?

2026-04-07

-

2023-08-29

-

2023-08-24

-

[ABAQUS] ABAQUS如何建模?ABAQUS有限元分析教程

2023-07-07

-

[ABAQUS] 有限元分析软件abaqus单位在哪设置?【操作教程】

2023-09-05

-

[ABAQUS] ABAQUS软件中Interaction功能模块中的绑定接

2023-07-19

-

[ABAQUS] Abaqus怎么撤回上一步操作?Abauqs教程

2024-05-01

-

[ABAQUS] abaqus里面s11、s12和u1、u2是什么意思?s和

2023-08-30

-

[ABAQUS] Abaqus单位对应关系及参数介绍-Abaqus软件

2023-11-20

-

[ABAQUS] Abaqus中的S、U、V、E、CF分别是什么意思?

2024-05-11

-

[ABAQUS] ABAQUS软件教程|场变量输出历史变量输出

2023-07-18

-

[行业资讯] 当 AI 遇到 CNC:全面革新机加工运营模式

2026-04-15

-

[行业资讯] 达索系统 SIMULIA PowerFLOW 技术论坛即将

2026-04-14

-

[行业资讯] 电磁场仿真工具CST studio suite正版价格多少

2026-04-13

-

2026-04-07

-

[行业资讯] 仿真模拟结果的准确性和可靠性,主要受哪些因素影响?

2026-04-07

-

[行业资讯] 工业领域常用的仿真软件有哪些?达索仿真软件代理商

2026-04-03

-

[行业资讯] 数字孪生赋能大湾区 2026 达索智造论坛佛山启幕

2026-04-02

-

[行业资讯] 达索系统SIMULIA Abaqus线性动力学分析技术论坛

2026-04-01

-

2026-03-30

-

[行业资讯] Abaqus有Mac版本吗?Abaqus代理商思茂信息

2026-03-27

地址: 广州市天河区天河北路663号广东省机械研究所8栋9层 电话:020-38921052 传真:020-38921345 邮箱:thinks@think-s.com