CST电磁仿真中,天线仿真匹配不好,能否加匹配电路调和驻波?

在射频天线设计与CST电磁仿真中,阻抗匹配是核心环节,驻波比(VSWR)则是衡量匹配效果的关键指标。很多工程师会遇到天线匹配不佳、驻波比超标(通常要求VSWR≤2)的问题,核心疑问是:能否通过添加匹配电路调和驻波?答案明确——可以,但需遵循科学的设计逻辑与仿真原则,盲目添加不仅无效,还可能引入额外损耗,影响天线辐射性能。

天线输入阻抗为复数值,理想状态下应与传输线特性阻抗(常见50Ω或75Ω)完全一致,此时驻波比趋近于1:1。但实际仿真中,因天线结构、尺寸、介质损耗、馈电方式或边界条件设置等问题,输入阻抗易偏离标准值,导致信号反射(S11参数>-10dB)、驻波比超标,造成能量浪费、辐射效率下降。

匹配电路的核心作用,是作为天线与传输线的“阻抗过渡桥梁”,通过电感(L)、电容(C)等无源元件,抵消天线阻抗的电抗分量、调整电阻分量,使变换后的阻抗接近传输线特性阻抗,从而减小反射、降低驻波比。在CST中添加匹配电路,需结合仿真工具功能与天线阻抗特性,精准建模优化。

CST Microwave Studio中,添加匹配电路主要有三种实用方法,适用于不同场景,结果可相互验证:

一是仿真后补加:天线三维模型仿真完成后,切换至Schematic窗口,添加电路激励端口与电感、电容等器件,更新仿真设置并运行电路分析,对比前后S参数曲线,观察驻波改善效果。

二是仿真前预设:在运行三维仿真前,通过Lunped Element图标在馈电处添加集总元件匹配电路,设置参数后直接仿真,可直接查看驻波是否达标。

三是多端口激励场景:仿真前添加多个离散激励端口,仿真后切换至Schematic窗口,参照第一种方法添加匹配电路,适用于阵列天线等复杂场景。

需注意,CST默认匹配器件为理想元件,若需贴近实际,可导入SPICE文件。匹配拓扑需结合天线阻抗:L型适用于点频匹配,结构简单但带宽窄;π型、T型自由度高,可实现宽频匹配,但损耗略大;阻抗差异大或宽频需求时,可采用多节级联网络,平衡带宽、损耗与复杂度。

添加匹配电路需遵循三大核心原则:首先,设计需基于天线实际阻抗特性,先通过CST提取阻抗、结合史密斯圆图分析失配原因,再针对性选择拓扑与参数,避免盲目尝试。其次,兼顾驻波改善与辐射性能,不可为追求低驻波过度复杂化电路,需同时监测驻波比、S11、增益等指标,建议将驻波比控制在1.5~2.0。再者,结合求解器与边界条件设置,馈电区域网格需精细,边界条件设为Open Space或PML,可利用参数扫描功能优化元件参数。

此外,需区分仿真与实物匹配的差异。仿真中元件为理想状态,无寄生参数,而实际中元件寄生效应、PCB布线会影响效果。因此仿真时可导入SPICE模型、添加寄生参数,仿真后结合实物测试微调参数。

需明确,匹配电路并非万能。若天线存在严重设计缺陷(如尺寸偏差、谐振频率偏移等),单纯依靠匹配电路难以达标,需先优化天线结构、尺寸、馈电方式等,再用匹配电路微调,才能实现最佳效果。

实际应用中,可利用CST的mini match宏快速生成匹配电路,结合参数扫描优化,也可与ADS等工具协同仿真,提升设计精度。

CST仿真中,天线匹配不佳时,添加匹配电路是有效调和手段,但需基于天线阻抗特性,遵循“先优化天线、再设计匹配”的原则,兼顾驻波与辐射性能,充分考虑仿真与实物差异,才能为实物制作奠定基础。

-

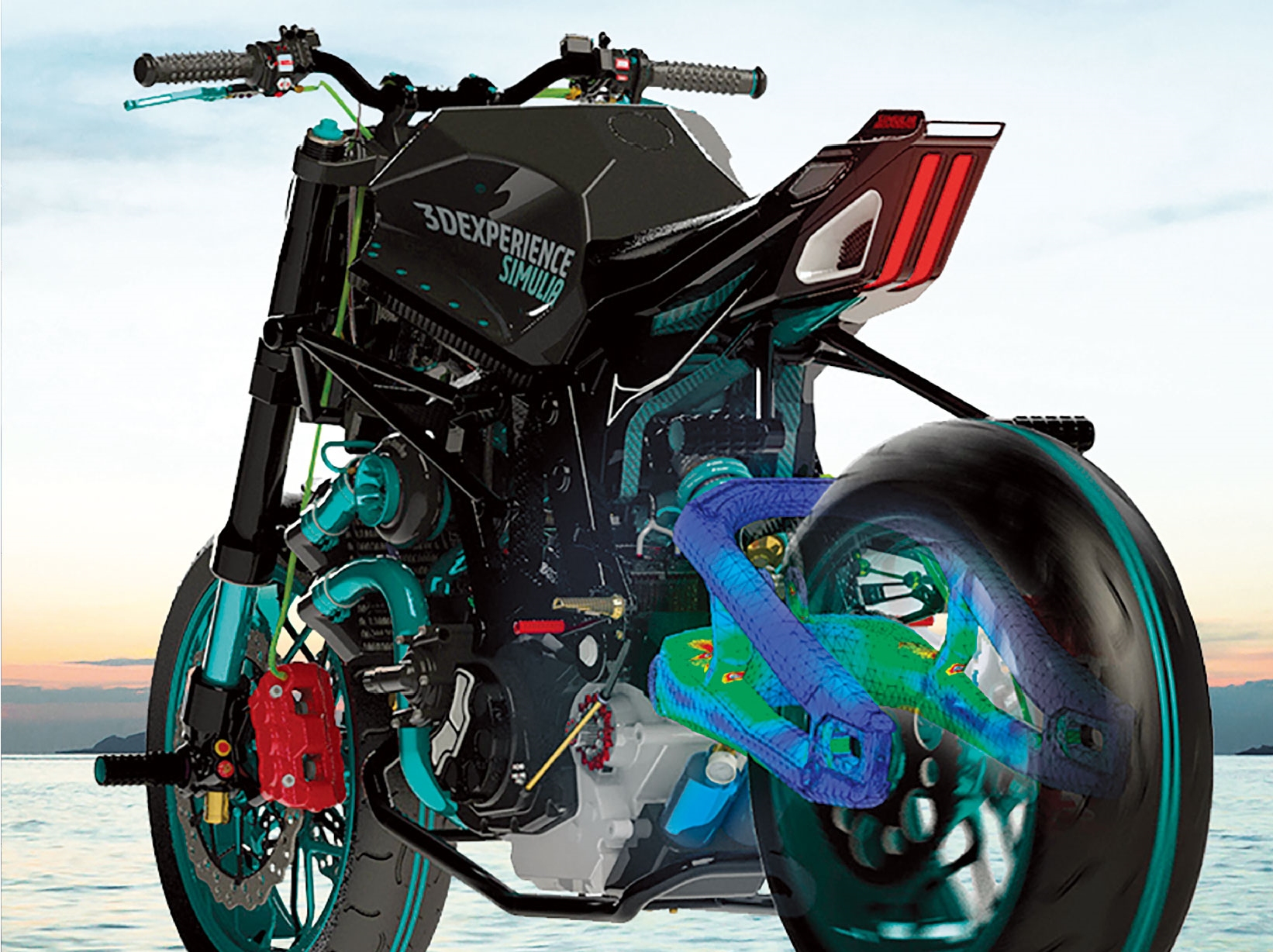

[行业资讯] 2026达索系统SIMULIA Abaqus结构仿真与优化

2026-05-12

-

[行业资讯] 工业AI,解锁产品创新与订单响应新范式|2026达索系统数

2026-05-12

-

[行业资讯] 达索系统SIMULIA Living Heart Mode

2026-05-08

-

[行业资讯] 当 AI 遇上 MBSE|赋能航空航天与汽车行业

2026-05-08

-

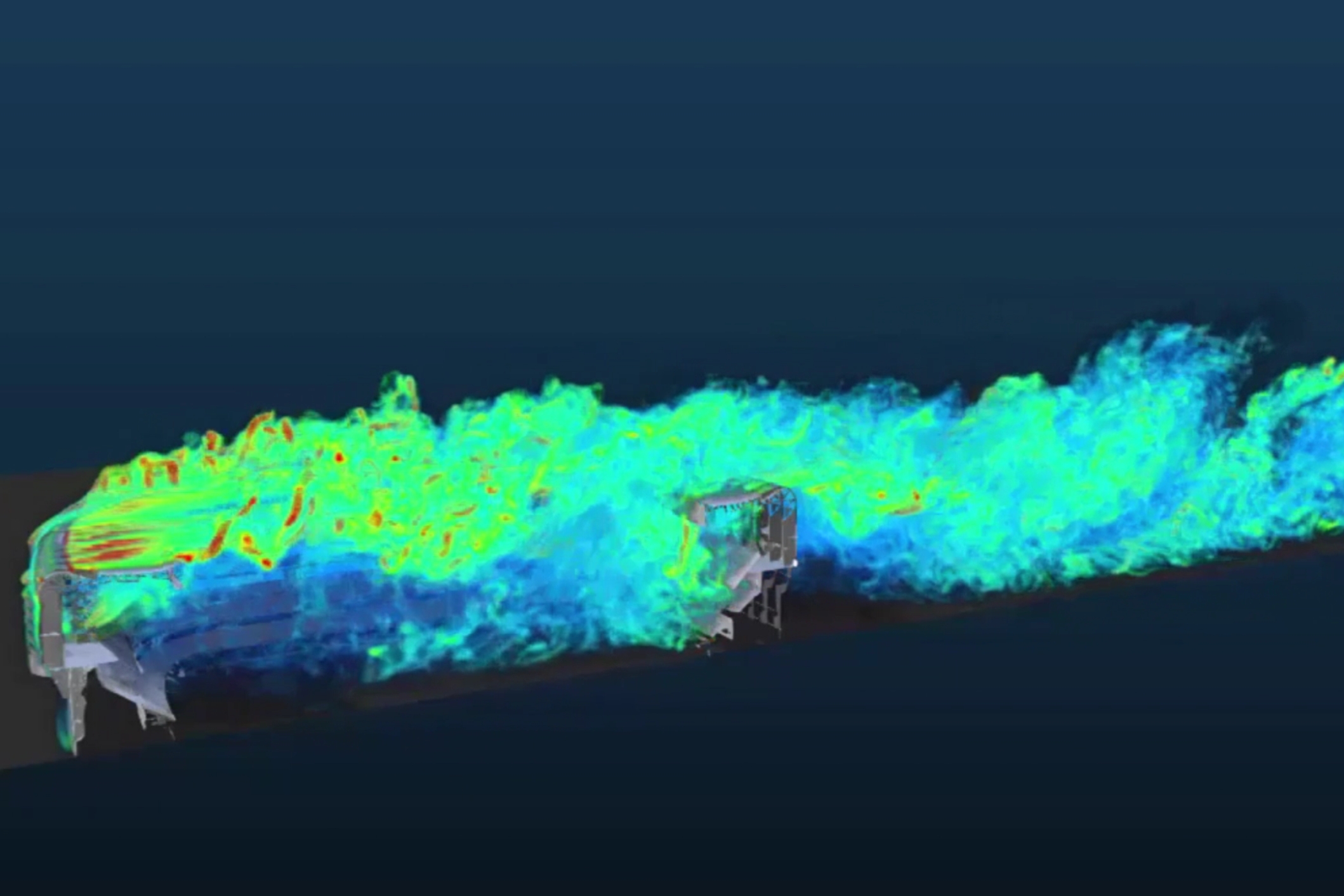

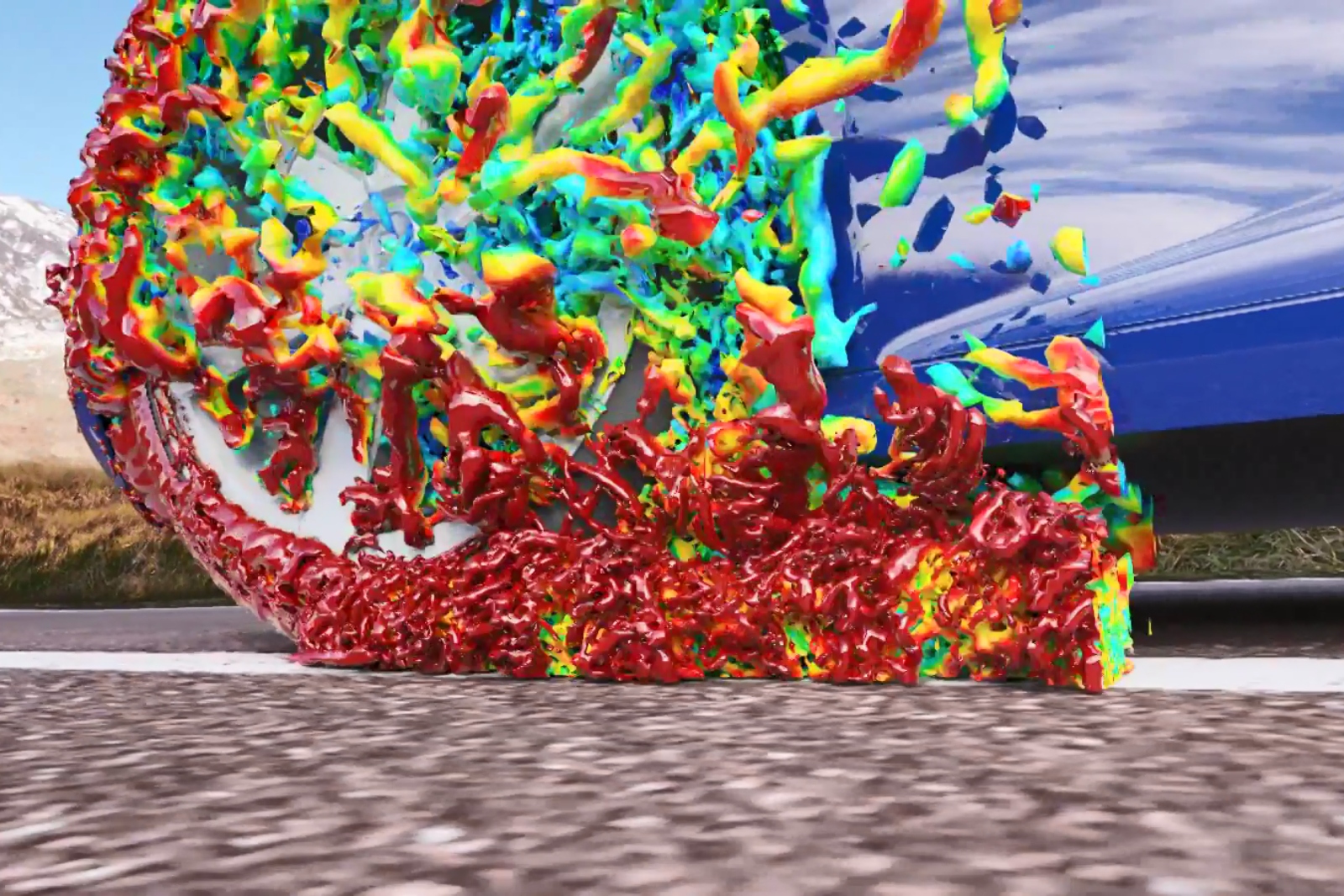

[行业资讯] 达索系统SIMULIA在交通工具外气动风噪的解决方案

2026-05-07

-

2026-05-04

-

[行业资讯] CST软件正版授权与达索一级代理商思茂信息介绍

2026-05-04

-

[行业资讯] 如何购买达索正版Abaqus?Abaqus核心代理商思茂信

2026-05-03

-

[行业资讯] 在仿真中,CST代表什么?CST电磁仿真工作室套装代理商

2026-05-03

-

[ABAQUS] Abaqus主要用来做什么?达索Simulia代理商

2026-04-30

-

2023-08-29

-

2023-08-24

-

[ABAQUS] ABAQUS如何建模?ABAQUS有限元分析教程

2023-07-07

-

[ABAQUS] 有限元分析软件abaqus单位在哪设置?【操作教程】

2023-09-05

-

[ABAQUS] ABAQUS软件中Interaction功能模块中的绑定接

2023-07-19

-

[ABAQUS] Abaqus怎么撤回上一步操作?Abauqs教程

2024-05-01

-

[ABAQUS] abaqus里面s11、s12和u1、u2是什么意思?s和

2023-08-30

-

[ABAQUS] Abaqus单位对应关系及参数介绍-Abaqus软件

2023-11-20

-

[ABAQUS] Abaqus中的S、U、V、E、CF分别是什么意思?

2024-05-11

-

[ABAQUS] ABAQUS软件教程|场变量输出历史变量输出

2023-07-18

-

[行业资讯] 2026达索系统SIMULIA Abaqus结构仿真与优化

2026-05-12

-

[行业资讯] 工业AI,解锁产品创新与订单响应新范式|2026达索系统数

2026-05-12

-

[行业资讯] 达索系统SIMULIA Living Heart Mode

2026-05-08

-

[行业资讯] 当 AI 遇上 MBSE|赋能航空航天与汽车行业

2026-05-08

-

[行业资讯] 达索系统SIMULIA在交通工具外气动风噪的解决方案

2026-05-07

-

[行业资讯] CST软件正版授权与达索一级代理商思茂信息介绍

2026-05-04

-

[行业资讯] 如何购买达索正版Abaqus?Abaqus核心代理商思茂信

2026-05-03

-

[行业资讯] 在仿真中,CST代表什么?CST电磁仿真工作室套装代理商

2026-05-03

-

[行业资讯] 达索系统SIMULIA Abaqus岩土工程与CEL技术培

2026-04-29

-

2026-04-27

地址: 广州市天河区天河北路663号广东省机械研究所8栋9层 电话:020-38921052 传真:020-38921345 邮箱:thinks@think-s.com